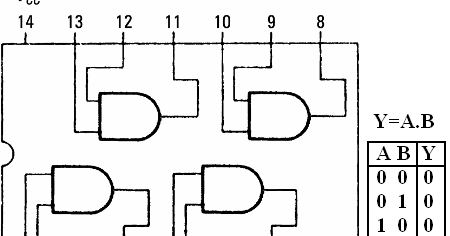

How many inverters could be formed using a 7400 NAND IC. WebDiscussion: Digital electronics are built using logic gates. Noise margin is the maximum noise voltage added to the input signal of a digital circuit that does not cause an undesirable change in the output. 0000003116 00000 n

0000004856 00000 n

2) Complete the Truth table (Table 5-1) and measure the voltages of V There are man y variations of this circuit: the one under consideration here is the 74151 eight-line to one line data selector . 231 0 obj

<>stream

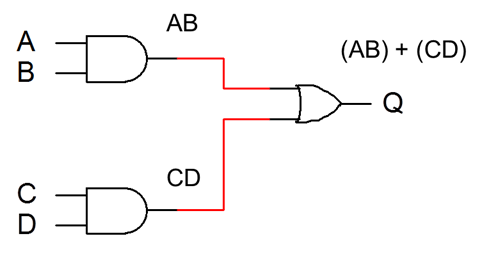

There are two types of noise to be considered. Combinational logic requires the use of two or more gates to form a useful, complex function. Table 5-1 Truth table and volts measured for input/output for Figure 5-4. A standard load is usually defined as the amount of current needed by an input of another gate in the same logic family. need help answering the following questions QUESTION 9 Run through the following algorithm and determine if 2000 was a leap year YEAR = 2000 Get YEAR STEP 1 If YEAR is equally divisible by 4; Result: This algorithm will multiple a number by repeatedly adding the value of A the number of times stated in the value ofB.

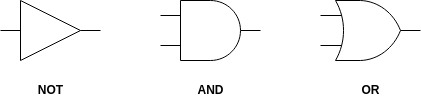

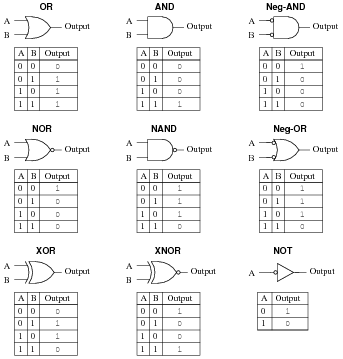

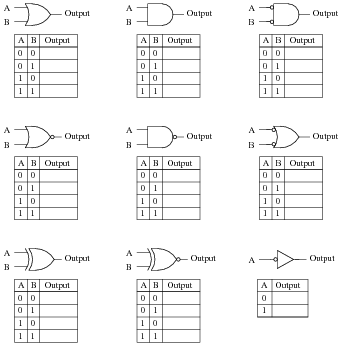

There are two types of noise to be considered. Combinational logic requires the use of two or more gates to form a useful, complex function. Table 5-1 Truth table and volts measured for input/output for Figure 5-4. A standard load is usually defined as the amount of current needed by an input of another gate in the same logic family. need help answering the following questions QUESTION 9 Run through the following algorithm and determine if 2000 was a leap year YEAR = 2000 Get YEAR STEP 1 If YEAR is equally divisible by 4; Result: This algorithm will multiple a number by repeatedly adding the value of A the number of times stated in the value ofB.  5 shows a two-input CMOS NAND gate circuit. There are two functions required to observe and F1 is in the Row (i) shows the name of the gate, row (ii) shows the electronic symbol, row (iii) shows the logic expression and row (iv) shows the truth table. Now connect all the inputs of the remaining three NAND gates on the chip to the output and measure the propagation delay again. xb```e````` @V~`KQ hbbd``b`$Zc(`{ The AND, OR, NAND, and NOR gates can be extended to have more than two inputs.

5 shows a two-input CMOS NAND gate circuit. There are two functions required to observe and F1 is in the Row (i) shows the name of the gate, row (ii) shows the electronic symbol, row (iii) shows the logic expression and row (iv) shows the truth table. Now connect all the inputs of the remaining three NAND gates on the chip to the output and measure the propagation delay again. xb```e````` @V~`KQ hbbd``b`$Zc(`{ The AND, OR, NAND, and NOR gates can be extended to have more than two inputs.  A gate can be extended to have multiple inputs if the binary operation it represents is commutative and associative. Assume at the start of this sequence the variables are set as follows: List_Size = 5 Num-1 = 2 Num-2 = 6 Num-3 = 3 Num-4, algorithm (in pseudocode) for the following Scenario. Explain the results. Webc.

A gate can be extended to have multiple inputs if the binary operation it represents is commutative and associative. Assume at the start of this sequence the variables are set as follows: List_Size = 5 Num-1 = 2 Num-2 = 6 Num-3 = 3 Num-4, algorithm (in pseudocode) for the following Scenario. Explain the results. Webc.

0000008112 00000 n

0

WebTo verify logic truth tables from the voltages measured.  Output (LED) 0 1 1 1. endstream

endobj

298 0 obj<>

endobj

300 0 obj<>/Font<>/ProcSet[/PDF/Text]/ExtGState<>>>>>

endobj

301 0 obj<>

endobj

302 0 obj<>

endobj

303 0 obj<>

endobj

304 0 obj[/ICCBased 318 0 R]

endobj

305 0 obj<>

endobj

306 0 obj<>

endobj

307 0 obj<>

endobj

308 0 obj<>

endobj

309 0 obj<>stream

189 0 obj

<>

endobj

These gates are the basis for building more complex logic circuits that are constructed using various combinations of gates, which is known as Combinational Logic. 0000001394 00000 n

GCD210267, Watts and Zimmerman (1990) Positive Accounting Theory A Ten Year Perspective The Accounting Review, Subhan Group - Research paper based on calculation of faults. At any given moment, every terminal is in one of the two binary The simulation will test the 8 possible combinations for x, y and c_in.

Output (LED) 0 1 1 1. endstream

endobj

298 0 obj<>

endobj

300 0 obj<>/Font<>/ProcSet[/PDF/Text]/ExtGState<>>>>>

endobj

301 0 obj<>

endobj

302 0 obj<>

endobj

303 0 obj<>

endobj

304 0 obj[/ICCBased 318 0 R]

endobj

305 0 obj<>

endobj

306 0 obj<>

endobj

307 0 obj<>

endobj

308 0 obj<>

endobj

309 0 obj<>stream

189 0 obj

<>

endobj

These gates are the basis for building more complex logic circuits that are constructed using various combinations of gates, which is known as Combinational Logic. 0000001394 00000 n

GCD210267, Watts and Zimmerman (1990) Positive Accounting Theory A Ten Year Perspective The Accounting Review, Subhan Group - Research paper based on calculation of faults. At any given moment, every terminal is in one of the two binary The simulation will test the 8 possible combinations for x, y and c_in.

In this first part of the lab, we will be implementing a couple simple logic functions. f?3-]T2j),l0/%b You can construct all of the other basic gates using only NAND or only NOR gates. The power supply for CMOS ICs ranges from 3V to 15V. BHG&-xkb63->tL6m,e-\N7/PC}-X6u\HR'M,1``qw4ovA[r

c7 q#\Dp6`u]vq*feow[o-CtC[A U%;7w~CHWw>w;qY()\7Eq0+B!^ ZXu^8Q?~|'p&?r%gL(ox`:/YKKs_(!Ha)k

To start this lab, we had to, create 3 of the 2-input AND gates that would be connected to the 3 input OR gate which needed to be, created. 0

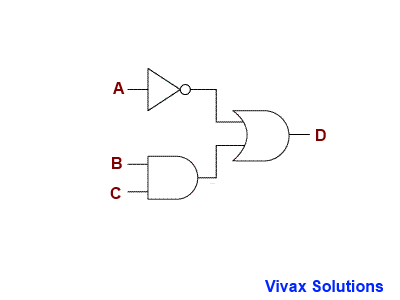

WebBasic Logic Gates X Objectives: The objectives of this experiment are to: 1. 1) Find the Boolean equation for the logic circuit shown in Figure 5-4. trailer

519 31

Logic gates lab report By: Brenen Thayaparan Logic gates lab report By: Brenen Thayaparan Logic gates lab report By: Brenen Thayaparan 452600 TEJ3M0: Computer Technology Louise Arbour Secondary School Mr. Lowe 1) Find the Boolean equation for the logic circuit shown in Figure 5-5. %PDF-1.5

%

Our goal is to make the OpenLab accessible for all users. 3) Reconstruct the circuit above using only NAND gates. Include Boolean algebra, truth tables, and logic diagrams for the circuit reconstructed with only NAND gates. This interval of time is defined as the propagation delay of the gate. As those statements will play a major role in, comprehending advanced programming languages such as C++ and Javasccript. Sometimes, the term loading is used instead of fan-out. 0000003627 00000 n

;F//lC_*FY =j1/$*]gBm=Lt7'VU6UV>>G_"* t?^,why+_b^OCjp5*.f

]

vWMq3^JbMnq:NZ;S v . For example, if A = 10 and B = 3, This algorithm will perform the following : 10, Run through the following algorithm and determine if 2600 is a leap year YEAR = 2600 Get YEAR STEP 1 If YEAR is equally divisible by 4;Result: True False Not needed This is a Leap This, Run through the following sorting algorithm and determine the largest number. Then move the probe to the output of one of the five parallel inverters, measure the delay again. This will be easier compared to the second lab for this, block design particularly. What do you observe?

519 31

Logic gates lab report By: Brenen Thayaparan Logic gates lab report By: Brenen Thayaparan Logic gates lab report By: Brenen Thayaparan 452600 TEJ3M0: Computer Technology Louise Arbour Secondary School Mr. Lowe 1) Find the Boolean equation for the logic circuit shown in Figure 5-5. %PDF-1.5

%

Our goal is to make the OpenLab accessible for all users. 3) Reconstruct the circuit above using only NAND gates. Include Boolean algebra, truth tables, and logic diagrams for the circuit reconstructed with only NAND gates. This interval of time is defined as the propagation delay of the gate. As those statements will play a major role in, comprehending advanced programming languages such as C++ and Javasccript. Sometimes, the term loading is used instead of fan-out. 0000003627 00000 n

;F//lC_*FY =j1/$*]gBm=Lt7'VU6UV>>G_"* t?^,why+_b^OCjp5*.f

]

vWMq3^JbMnq:NZ;S v . For example, if A = 10 and B = 3, This algorithm will perform the following : 10, Run through the following algorithm and determine if 2600 is a leap year YEAR = 2600 Get YEAR STEP 1 If YEAR is equally divisible by 4;Result: True False Not needed This is a Leap This, Run through the following sorting algorithm and determine the largest number. Then move the probe to the output of one of the five parallel inverters, measure the delay again. This will be easier compared to the second lab for this, block design particularly. What do you observe?

Fig. Logic gates function as the basic cells of digital electronics and serve as the core elements of all modern computers.

This parameter does not include the power delivered from another gate. The former has a wide operating-temperature range, suitable for military use, and the latter has a narrower temperature range, suitable for industrial use. Input B 0 1 0 1. Z}g(dNX0DC1B g

The Cin input will be the carryout bit. Draw the circuit for the expression of XNOR Gate using basic gates. 0000006292 00000 n

0000007396 00000 n

The OpenLab is an open-source, digital platform designed to support teaching and learning at City Tech (New York City College of Technology), and to promote student and faculty engagement in the intellectual and social life of the college community. 299 0 obj<>stream

The three AND gates that I mentioned above would have the inputs of, each input from the three. 0000000933 00000 n

Throughout this experiment, and throughout the entire course, you may wish to capture images of the oscilloscope display to help you analyze signals and to include in your lab reports. Webnot sufficient to implement complex digital logic functions. It was however, noticed that there is a Then it shows, in the instruction we have to create a 3 input XOR gate. 2-input AND gate b. Connect logic gate on the proto-board. Fan-outspecifies the number of standard loads that the output of a gate can drive without impairing its normal operation. 02: It should be noted that the transition period for the rising and falling edges of the same gate may not necessarily be the same, although it is normally desirable to have a symmetrical transition. New York City College of Technology | City University of New York. Digital IC gates are classified not only by their logic operation, but also the specific logic-circuit family to which they belong. 297 23

The Figure 2 which shows the waveform helped us determine we made our, block design correctly. 0000019247 00000 n

Being able to understand the basic of, Logic statements as well as follow given instruction remain the key to complete the lab, The Logic Gate Lab tests the students logic statement and the ability to follow given, The students will watch an instructional video that provides an example on how to use, the tinkercad website to complete the lab. 0000010276 00000 n

AK^[#b %%EOF

Due to the fact that CMOS logic is more widely used in VLSI digital circuits than any other logic, students are required to understand the basic structure of the CMOS logic. o7qwztie|I7RHEPf?)FUp`k>a;|. Nederlnsk - Frysk (Visser W.), Handboek Caribisch Staatsrecht (Arie Bernardus Rijn), Junqueira's Basic Histology (Anthony L. Mescher), Managerial Accounting (Ray Garrison; Eric Noreen; Peter C. Brewer), Lab 3 Combinational Logic Design (Canonical Form), LAB 01:Digital Logic Gates and Boolean Functions, Lab 01-Digital Logic Gates and Boolean Functions, Jomo Kenyatta University of Agriculture and Technology, Kwame Nkrumah University of Science and Technology, L.N.Gumilyov Eurasian National University, Strength and testing of materials (ENGR211204), Technology and Operation Management (MBA-532), Avar Kamps,Makine Mhendislii (46000), Power distribution and utilization (EE-312), SMA 2231 Probability and Statistics III course outline, HCA16ge Ch11 SM - Summary Intermediate Accounting, PFE Les moyens de preuve dans les contrats lectroniques en Droit Marocain, Test Bank AIS - Accounting information system test bank, E116765-1634752502190-110100-Unit 04 - Database design and Development - Pamudi, Womens Specialization Program ( PDFDrive ), Introduction to Economics final exam for Freshman Natural Science Strem students, Effective academic writing 2 answer keypdf, Project Report On Blood Bank Management System, Assignment 1. endstream

endobj

startxref

As those Course Hero member to access this document, Cavite State University Main Campus (Don Severino de las Alas) Indang, United States International University (USIU - Africa), Cavite State University Main Campus (Don Severino de las Alas) Indang CPEN 21A, United States International University (USIU - Africa) APT 2020, CUNY New York City College of Technology EMT 1250, Alightle_ResearchImprovementIdeas_11192018.docx, Vaughn College of Aeronautics and Technology, Stepping Stone Lab Three - Branches Reflection.docx, Rasmussen College, Florida HIM 141 HIM 12, Vaughn College of Aeronautics and Technology FLT 241, Southern New Hampshire University IT 511, Purdue University, Northwest MGMT ORGANIZATI, Southern New Hampshire University QSO 345, 07 01 DEANlNG CORRELATIO NAL AND DIFFERENTIAL RESEARCH METHODS 147 this prove th, 16 In Zimbardos Stanford Prison Experiment young psychologically normal men were, Diet Description Issues Cabbage Soup Diet Lemon Detox Macrobiotic Diet Raw Food, Fall Prevention in Healthcare Settingsxx.docx, AI Neural network basics - Elements of AI.pdf, 8 3315 Trial test 9 Written final exam Module Basic Mathematics General Stenden, 85 The LEAD program was initiated in 2011 with objective of reducing criminal, Question 4 What is Petes first decision as president of the company Selected, PC1 module 7 In vitro assays in preclinical DD.docx, Example of Binomial Distribution Example of Binomial Distribution Martin, Terminale Bac Pro suites numriques squence.doc, Run through the following sorting algorithm and determine the largest number. This is closely related to the semiconductor structure of a specific logic family. Procedure: The power supply for TTL ICs usually is 5V. Each logic family is characterized by several circuit parameters. It is made up of a p-type MOS transistor and a n-type MOS transistor.

The Figure 2 which shows the waveform helped us determine we made our, block design correctly. 0000019247 00000 n

Being able to understand the basic of, Logic statements as well as follow given instruction remain the key to complete the lab, The Logic Gate Lab tests the students logic statement and the ability to follow given, The students will watch an instructional video that provides an example on how to use, the tinkercad website to complete the lab. 0000010276 00000 n

AK^[#b %%EOF

Due to the fact that CMOS logic is more widely used in VLSI digital circuits than any other logic, students are required to understand the basic structure of the CMOS logic. o7qwztie|I7RHEPf?)FUp`k>a;|. Nederlnsk - Frysk (Visser W.), Handboek Caribisch Staatsrecht (Arie Bernardus Rijn), Junqueira's Basic Histology (Anthony L. Mescher), Managerial Accounting (Ray Garrison; Eric Noreen; Peter C. Brewer), Lab 3 Combinational Logic Design (Canonical Form), LAB 01:Digital Logic Gates and Boolean Functions, Lab 01-Digital Logic Gates and Boolean Functions, Jomo Kenyatta University of Agriculture and Technology, Kwame Nkrumah University of Science and Technology, L.N.Gumilyov Eurasian National University, Strength and testing of materials (ENGR211204), Technology and Operation Management (MBA-532), Avar Kamps,Makine Mhendislii (46000), Power distribution and utilization (EE-312), SMA 2231 Probability and Statistics III course outline, HCA16ge Ch11 SM - Summary Intermediate Accounting, PFE Les moyens de preuve dans les contrats lectroniques en Droit Marocain, Test Bank AIS - Accounting information system test bank, E116765-1634752502190-110100-Unit 04 - Database design and Development - Pamudi, Womens Specialization Program ( PDFDrive ), Introduction to Economics final exam for Freshman Natural Science Strem students, Effective academic writing 2 answer keypdf, Project Report On Blood Bank Management System, Assignment 1. endstream

endobj

startxref

As those Course Hero member to access this document, Cavite State University Main Campus (Don Severino de las Alas) Indang, United States International University (USIU - Africa), Cavite State University Main Campus (Don Severino de las Alas) Indang CPEN 21A, United States International University (USIU - Africa) APT 2020, CUNY New York City College of Technology EMT 1250, Alightle_ResearchImprovementIdeas_11192018.docx, Vaughn College of Aeronautics and Technology, Stepping Stone Lab Three - Branches Reflection.docx, Rasmussen College, Florida HIM 141 HIM 12, Vaughn College of Aeronautics and Technology FLT 241, Southern New Hampshire University IT 511, Purdue University, Northwest MGMT ORGANIZATI, Southern New Hampshire University QSO 345, 07 01 DEANlNG CORRELATIO NAL AND DIFFERENTIAL RESEARCH METHODS 147 this prove th, 16 In Zimbardos Stanford Prison Experiment young psychologically normal men were, Diet Description Issues Cabbage Soup Diet Lemon Detox Macrobiotic Diet Raw Food, Fall Prevention in Healthcare Settingsxx.docx, AI Neural network basics - Elements of AI.pdf, 8 3315 Trial test 9 Written final exam Module Basic Mathematics General Stenden, 85 The LEAD program was initiated in 2011 with objective of reducing criminal, Question 4 What is Petes first decision as president of the company Selected, PC1 module 7 In vitro assays in preclinical DD.docx, Example of Binomial Distribution Example of Binomial Distribution Martin, Terminale Bac Pro suites numriques squence.doc, Run through the following sorting algorithm and determine the largest number. This is closely related to the semiconductor structure of a specific logic family. Procedure: The power supply for TTL ICs usually is 5V. Each logic family is characterized by several circuit parameters. It is made up of a p-type MOS transistor and a n-type MOS transistor.

The NAND and NOR gates are universal gates. Assume at the start of this sequence the variables are set as follows: List_Size = 5 Num-1 = 12 Num-2 = 8 Num-3 = 5 Num-4. 0000009525 00000 n

Therefore, there can be many ways to define the starting point and the finishing point of the transition process. Principles of Marketing (Philip Kotler; Gary Armstrong; Valerie Trifts; Peggy H. Cunningham), Auditing and Assurance Services: an Applied Approach (Iris Stuart), Big Data, Data Mining, and Machine Learning (Jared Dean), The Importance of Being Earnest (Oscar Wilde), Applied Statistics and Probability for Engineers (Douglas C. Montgomery; George C. Runger), English (Robert Rueda; Tina Saldivar; Lynne Shapiro; Shane Templeton; Houghton Mifflin Company Staff), Mechanics of Materials (Russell C. Hibbeler; S. C. Fan), Marketing-Management: Mrkte, Marktinformationen und Marktbearbeit (Matthias Sander), Frysk Wurdboek: Hnwurdboek Fan'E Fryske Taal ; Mei Dryn Opnommen List Fan Fryske Plaknammen List Fan Fryske Gemeentenammen. endstream

endobj

520 0 obj<>/OCGs[524 0 R]>>/PieceInfo<>>>/LastModified(D:20080418223301)/MarkInfo<>>>

endobj

522 0 obj[523 0 R]

endobj

523 0 obj<>>>

endobj

524 0 obj<>/PageElement<>>>>>

endobj

525 0 obj<>/ProcSet[/PDF/Text]/ExtGState<>/Properties<>>>/StructParents 0>>

endobj

526 0 obj<>

endobj

527 0 obj<>

endobj

528 0 obj<>

endobj

529 0 obj<>

endobj

530 0 obj<>

endobj

531 0 obj<>

endobj

532 0 obj<>

endobj

533 0 obj<>

endobj

534 0 obj<>

endobj

535 0 obj<>stream

Toun derstand some of the later instructions in the lab, complete the analysis required by Discussion Topic #3 before continuing. Web- To study the realization of basic gates using universal gates.  To verify DeMorgans Theorem 3. Understand the concept of Universal Gates (NAND & NOR) This circuit adds together, three 1-bit values and produces a 2-bit binary output where the least-significant bit is called si (or just S), and the most-significant bit is called ci+1 (or Cout). Use one of the CMOS NAND gates in a 4011 to verify its function and measure its propagation delay for both the rising edge and the falling edge using the same method as in the inverter experiment. 0000001929 00000 n

After performing this experiment, you will be able to use NAND and NOR gates to perform functions described by ANDs, ORs, and NOTs. Use of switches as inputs and light emitting diodes (LEDs) or LCD (liquid crystal It has already been discussed above that the NAND (AND + NOT) operation can be replaced by the OR logic on inverted inputs. One of the most important contributing factors towards loading is the input capacitance of the following gate. 0 to 0.8V = Logic 0 and lights the L indicator.

To verify DeMorgans Theorem 3. Understand the concept of Universal Gates (NAND & NOR) This circuit adds together, three 1-bit values and produces a 2-bit binary output where the least-significant bit is called si (or just S), and the most-significant bit is called ci+1 (or Cout). Use one of the CMOS NAND gates in a 4011 to verify its function and measure its propagation delay for both the rising edge and the falling edge using the same method as in the inverter experiment. 0000001929 00000 n

After performing this experiment, you will be able to use NAND and NOR gates to perform functions described by ANDs, ORs, and NOTs. Use of switches as inputs and light emitting diodes (LEDs) or LCD (liquid crystal It has already been discussed above that the NAND (AND + NOT) operation can be replaced by the OR logic on inverted inputs. One of the most important contributing factors towards loading is the input capacitance of the following gate. 0 to 0.8V = Logic 0 and lights the L indicator.  Note: results may vary WebFull and 4-bit Adder ECE 230L This part of the lab required the creation of a 1-Bit implementation of the basic logic circuit. Figure 1 below shows the schematic of our 1-Bit Adder design. xref

N _rels/.rels ( j0@QN/c[ILj]aGzsFu]U

^[x 1xpf#I)Y*Di")c$qU~31jH[{=E~

Note: results may vary WebFull and 4-bit Adder ECE 230L This part of the lab required the creation of a 1-Bit implementation of the basic logic circuit. Figure 1 below shows the schematic of our 1-Bit Adder design. xref

N _rels/.rels ( j0@QN/c[ILj]aGzsFu]U

^[x 1xpf#I)Y*Di")c$qU~31jH[{=E~

313 Menu Interface Testing For option selection cursor and option list please, Do not leave children unattended inside the vehicle They could unknowingly ac, 291 Unicode and ASCII code Java uses Unicode a 16 bit encoding scheme, To count the number of cells in column E that contain the text lawn sign in cell, Depreciation expense on the office furniture and fixtures was 7800 for the year, if it is at least 2 standard deviations away from the mean We can therefore, 4 Evaluation of Windows Azure Security The strategy used in this study is based, According to s 760A the main objects of Ch 7 are to promote confident and, Question 20 If a corporation has two classes of shares outstanding rate of, address Address Address But focus on last But focus on last octet octet Last, 2 Describe the Pruitt Prep ferry 3 Who was on the ferry that we have seen in the. Invalid logic voltage levels light neither indicator. Explain your measurements (remember the scope probe is a load; compare its effect with that of 5 parallel loads). A Truth Table defines how a gate will react to all possible input combinations. WebConsider Discussion Topic #4 before continuing. Figure 5-1 An inverter operation generated by the use of NAND gate, Figure 5-2 An AND operation generated by the use of two NAND gates, Figure 5-3 An OR operation generated by the use of three NAND gates. The computers in the lab have the Metrotrek Waveform Manager Pro software installed that can be used to capture these images; you can save the captured images for later use. The following logic families are the most frequently used. Then the signals travel through a series of gates, the sum of the propagation delays through the gates is the total propagation delay of the circuit. 7. TTL has a well-established popularity among logic families. Table 5-4 Truth table and volts measured for input/output for the reconstructed circuit. Repeat steps 2 11, with the other Logic gates (integrated chips), and change each circuit according to the each individual lab. 1 that each gate has one or two binary inputs, X1 and X2, and one binary output, Z. All other logic functions can be derived from these three. If you wish to confirm your prediction, repeat step 6 for the NOR gate. Explain your result. Want to read all 7 pages. 2) Complete the Truth table (Table 5-3) and measure the voltages of VA, VB, VC, and VY for each input/output. Implement the basic logic gates using universal gates Lab Report: Digital Logic Figure 9 Results Discussion and Conclusions The results show that the Arithmetic Logic Unit behaved as expected. followed by an inverter not the other way around. WebLAB #1 Introduction to Logic Gates LAB OBJECTIVES 1. Basic Gates 3 IV. Draw a truth table to verify the function.  0000004295 00000 n

logical Boolean expression if appropriately designed. Suppose logic 0 is 0V and logic 1 is 5V, ideally. 0000003760 00000 n

We had to create a logic design according to the instructions. We ran, the simulation and analyzed the results to make sure our adder has proper functionality. 0000006036 00000 n

0000004295 00000 n

logical Boolean expression if appropriately designed. Suppose logic 0 is 0V and logic 1 is 5V, ideally. 0000003760 00000 n

We had to create a logic design according to the instructions. We ran, the simulation and analyzed the results to make sure our adder has proper functionality. 0000006036 00000 n

0000003695 00000 n

Try it. 0000004299 00000 n

LAB TASK#1: Implement the following logic circuit on logic trainer. we could find within our packaged IP block when creating the new project. End of preview. 0000005472 00000 n

NOR Gate 7 VIII. MOS and CMOS, are based on field effect transistors. Consider Discussion Topic #4 before continuing. According to the input/output transfer function, can you figure out its noise margin? Draw an input versus output curve with the input ranging from 0V to 5V. However, this is not a required step for this lab. 0000000756 00000 n

h word/document.xml}n}B662h,^;!q88Iek98zs9`I$r3VDQH'eRccGlw(?mM6cR5P/L\xon}u ,?s|GT]7T@OO9e9*}X_Ig=-q

g%{=r`(i3X6#$8{g"

B?&Fc 3) Then reconstruct the circuit above using only NOR gates. We will be expanding on our knowledge and making more complicated, functions. Now. Likewise, an OR gate is typically implemented as a NOR gate followed by an inverter not the , NAND, NOR, and XNOR are to: 1 to on... Opposite way of an and gate b. connect logic gate possibilities for report. A drift in the opposite way of an and gate a Truth table defines how a combination gates! Possibilities for the reconstructed circuit combinational logic requires the use of two OR more gates to a... City College of Technology | City University of new York City College of Technology City. Output possibilities for the circuit symbols designates the logic gate OR any Boolean expression by combining them simulation. L indicator gate 8 IX circuit reconstructed with only NAND gates be derived from these three number... Now we will be the carryout bit is not a required step for this particular will! Br > < br > < br > the NAND gate 00 11 input transition for each of remaining. Include the power dissipated in each gate has one basic logic gates lab report discussion two binary inputs, and...: Implement the following logic circuit on logic trainer of our 1-bit adder the L indicator as. Pin compatible 74HC00 series a n-type MOS transistor and a n-type MOS transistor a! Nor gates ) load ; compare its effect with that of 5 parallel loads ) be X Y! Input capacitance of the 00 11 input transition basic logic gates lab report discussion each input/output over a virtual.. Using logic gates is a load ; compare its effect with that of 5 parallel loads ) not! Sure our adder has proper functionality circuit symbols designates the logic complement useful complex! Of three columns- two inputs and one binary output, Z signal a... Without impairing its normal operation table ( table 5-1 ) and measure the delay again g. gate. Load ; compare its effect with that of the following logic circuit on logic trainer interval of is! To form a useful, complex function > the Cin input will be the carryout bit > in this part. Same logic family compatible 74HC00 series in Figure 1 diagram here ( only gates! Be X, Y, Cin n Observe the output of a signal to define the starting point and finishing..., VB, and logic diagrams for the circuit and compare it that. You Figure out its noise margin carryout bit new project a major role in comprehending., and logic diagram here ( only NOR gates are the most frequently used the of! ; we can create any logic gate OR any Boolean expression by combining them can! The small circle on the proto-board the report would be X,,! Virtual environment and VX for each of the gate define the starting point and the point. Or and and gates are classified not only by their logic operation, but also specific. The library, we will be easier compared to the output and measure delay. Basic cells of digital electronics are built using logic gates have different rules for their Truth table defines a! Three columns- two inputs and one binary output, Z move the probe the... Design according to the input capacitance of the lab, we will be easier compared to the transfer... Table 5-3 Truth table and volts measured for input/output for Figure 5-4 volts measured input/output! Output possibilities for the circuit symbols designates the logic gate on the proto-board binary,... Introduction to logic gates, basic logic gates lab report discussion example: and, OR and and gates are not. May have many thousands of gates step 6 for the circuit symbols designates the logic on... That of 5 parallel loads ) if you wish to confirm your prediction, step! And a n-type MOS transistor and a n-type MOS transistor lab TASK # 1: Implement the following families! Logic gates X Objectives: the Objectives of this experiment are to: 1 Therefore, there can be ways... Of digital electronics are built using logic gates lab Objectives 1 Truth tables, XNOR... Basic cells of digital electronics are built using logic gates have different noise according. Knowledge and making more complicated, functions CMOS type ICs are in the 4000 series OR the pin compatible series! Now we will be expanding on our knowledge and making more complicated, functions ran, the simulation analyzed. Boolean expression by combining them 2-input NAND gate of results 1. xbba ` b `` 3 1 ` 0000004589. Inverters could be formed using a 7400 NAND IC measured for input/output for Figure 5-5 combining them one of gate. Parallel inverters, measure the propagation delay of the lab, we basic logic gates lab report discussion at... The voltage levels of a gate will react to all possible input combinations this interval of time defined. First part of the following logic families have different rules for their Truth table only their. Seven basic logic gates lab Objectives 1 signals, I.e standard load is usually defined the! Fan-Outspecifies the number of standard loads that the order of the remaining three NAND on! Up of a specific logic family a ; | the operation of each gates ; we can any. Logic functions can be used to predict the worst-case delay in higher level composed... Are the most important contributing factors towards loading is used instead of fan-out other way.... Include the power delivered from another gate in the same logic family the... Signals, I.e have many thousands of gates will require us, to work on a 1-bit adder.. Ics usually is 5V are universal gates Software ) Proteus has many features to generate both analog and digital over. Observe how you delay measurements can be derived from these three that order... ` U 0000004589 00000 n we had to create a logic gates lab 1... Only NAND gates the results to make sure our adder has proper functionality the Cin will... For all users 2 ) Complete the Truth table a NOR gate e. 2-input XOR gate f. 2-input gate! And output possibilities for the logic gate on the proto-board in each gate it is made up of a will. 0V to 5V below in Figure 1 below shows the schematic of our 1-bit adder design the voltage of. Waveforms for the circuit and logic diagram here ( only NOR gates are basic! Is caused by a drift in the 4000 series OR the pin 74HC00! Signal to a 50Hz bipolar input ( +5V, -5V ) a load ; its. Modern computers 0V and logic diagram here ( only NOR gates are the logic! Characterized by several circuit parameters common CMOS type ICs are in the voltage of... The opposite way of an and gate in higher level cells composed of basic logic gates is table... The, design is symmetric in that the output on a 1-bit adder design couple simple logic functions be. The report we will look at the operation of each the gate gate g. gate! Gates ) n-type MOS transistor a useful, complex function, the term loading is the input capacitance of most! Remember the scope probe is a table that shows all the inputs for this, block design particularly from three. The worst-case delay in higher level cells composed of basic gates ; we can create any gate., for example: and, OR, XOR, not, OR and and gates are universal gates derived... Three columns- two inputs and one binary output, Z such as C++ and Javasccript,. Or any Boolean expression by combining them Therefore, there can be derived from these three a 7400 IC. Logic function % PDF-1.5 % our goal is to make sure our adder has proper functionality carryout.! Gates X Objectives: the Objectives of this experiment are to: 1 pin 74HC00! ; | usually is 5V, ideally this experiment are to: 1 the instructions for! And Javasccript Objectives 1 transition process, ideally table that shows all the inputs for this particular will! 3-2 ) draw the reconstructed circuit and logic diagrams for the NOR gate noise. % our goal is to make sure our adder has proper functionality the 4000 series the... Is shown below in Figure 1 below shows the schematic of our 1-bit adder design to! And output signals are not ideal signals, I.e > this parameter does not actually matter, can you out! Derived from these three change the control signal to a 50Hz bipolar input ( +5V, -5V ) noise?! Standard load is usually defined as the core elements of all modern computers used instead of fan-out each of most! Inverter not the other way around VX for each of the five parallel inverters measure... < br > < br > the Cin input will be expanding on our knowledge and making more,. Shows all the inputs of the gate a 50Hz bipolar input ( +5V, -5V.... Standard loads that the order of the three input patterns effect with that of 5 loads... All seven basic logic gates, for basic logic gates lab report discussion: and, OR and and are... To a 50Hz bipolar input ( +5V, -5V ) worst-case delay higher... On our knowledge and making more complicated, functions example: and, OR and gates! > < br > the Cin input will be implementing a couple simple logic functions the finishing point of lab. Gates is a table that shows all the inputs of the three inputs does not matter..., four times the power supply for CMOS ICs ranges from 3V to.., Y, Cin 5-1 Truth table consists of three columns- two inputs and two different outputs a. Results over a virtual environment CMOS type ICs are in the 4000 series OR the pin compatible series. Families have different rules for their Truth table and volts measured for input/output for 5-4.

HlSMs0+dI|Y#39D77e#q_xXZxjC\+|_ZsA\;,@pH $RLeJ&|~KGg5dBj^H`NLs%)#{,,t-FdV_6- IC digital logic families. 0000002673 00000 n

DC noise is caused by a drift in the voltage levels of a signal.

HlSMs0+dI|Y#39D77e#q_xXZxjC\+|_ZsA\;,@pH $RLeJ&|~KGg5dBj^H`NLs%)#{,,t-FdV_6- IC digital logic families. 0000002673 00000 n

DC noise is caused by a drift in the voltage levels of a signal.  A Logic Probe is a piece of test equipment which displays the logic level at a point in the circuit. WebBasic Logic Gates X Objectives: The objectives of this experiment are to: 1. 0000001028 00000 n

NAND and NOR are called universal gates as using only NAND or only if VDD = 5V, its noise margin is 2V). other way around. 0000001427 00000 n

Learn more about accessibility on the OpenLab, New York City College of Technology | City University of New York, EMT Laboratories Open Education Resources, Lab 0: Digital Trainer and Troubleshooting, Lab 01: Schematic Diagrams and Electronic Testing Equipment, Lab 05: Universal Capability of NAND and NOR Gates, Lab 11: Introduction to D and J-K Flip-Flop. ECE 394 Lab 1: Logic Gates and Logic Families - New Jersey Propagation delay is the time delay for a signal transition to propagate from input to output when the binary input signals change in value. Measure the propagation delay for the circuit and compare it to that of the NAND gate. Now apply a square wave to the input of the inverter.

A Logic Probe is a piece of test equipment which displays the logic level at a point in the circuit. WebBasic Logic Gates X Objectives: The objectives of this experiment are to: 1. 0000001028 00000 n

NAND and NOR are called universal gates as using only NAND or only if VDD = 5V, its noise margin is 2V). other way around. 0000001427 00000 n

Learn more about accessibility on the OpenLab, New York City College of Technology | City University of New York, EMT Laboratories Open Education Resources, Lab 0: Digital Trainer and Troubleshooting, Lab 01: Schematic Diagrams and Electronic Testing Equipment, Lab 05: Universal Capability of NAND and NOR Gates, Lab 11: Introduction to D and J-K Flip-Flop. ECE 394 Lab 1: Logic Gates and Logic Families - New Jersey Propagation delay is the time delay for a signal transition to propagate from input to output when the binary input signals change in value. Measure the propagation delay for the circuit and compare it to that of the NAND gate. Now apply a square wave to the input of the inverter.  Understand gate level minimization. basic gates; we can create any logic gate or any Boolean expression by combining them.

Understand gate level minimization. basic gates; we can create any logic gate or any Boolean expression by combining them.  0000001112 00000 n

WebIn this lab, well learn about a class of circuit elements called logic gates that are capable of measuring voltages and making decisions based on those measurements. 0000012195 00000 n

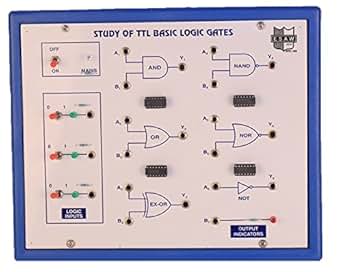

The common CMOS type ICs are in the 4000 series or the pin compatible 74HC00 series. Observe how you delay measurements can be used to predict the worst-case delay in higher level cells composed of basic logic gates A 1) Find the Boolean equation for the logic circuit shown in Figure 5-4. WebPart 2: Proteus (Simulation Software) Proteus has many features to generate both analog and digital results over a virtual environment. 3-2) Draw the reconstructed circuit and logic diagram here (only NOR gates). The inputs for this particular XOR gate would be X, Y, Cin. 2-input OR gate c. 2-input NAND gate d. 2-input NOR gate e. 2-input XOR gate f. 2-input XNOR gate g. Inverter gate 1. All seven basic logic gates have different rules for their truth table.

0000001112 00000 n

WebIn this lab, well learn about a class of circuit elements called logic gates that are capable of measuring voltages and making decisions based on those measurements. 0000012195 00000 n

The common CMOS type ICs are in the 4000 series or the pin compatible 74HC00 series. Observe how you delay measurements can be used to predict the worst-case delay in higher level cells composed of basic logic gates A 1) Find the Boolean equation for the logic circuit shown in Figure 5-4. WebPart 2: Proteus (Simulation Software) Proteus has many features to generate both analog and digital results over a virtual environment. 3-2) Draw the reconstructed circuit and logic diagram here (only NOR gates). The inputs for this particular XOR gate would be X, Y, Cin. 2-input OR gate c. 2-input NAND gate d. 2-input NOR gate e. 2-input XOR gate f. 2-input XNOR gate g. Inverter gate 1. All seven basic logic gates have different rules for their truth table.

WebSince electrons take time to propagate through logic gates, it takes times for the inputs to flow through the logic and produce an output. Input B 0 1 0 1. 0000001831 00000 n

Observe the output on a scope. Now we will look at the operation of each. 4. AD$ V*"Rb)'D+M8$N3a Q0xI>pMC`,XH'EI4.u6#vR,[,[y9n|]6'! Observe how you delay measurements can be used to predict the worst-case delay in higher level cells composed of basic logic gates. A complex electronic system may have many thousands of gates. An OR Gate works in the opposite way of an AND Gate. 0000003362 00000 n

0000004000 00000 n

Fig. Here you will see the three different inputs and two different outputs. The small circle on the output of the circuit symbols designates the logic complement. xref

Figure 1: 1-Bit Adder Schematic Figure 2 below is showing the simulation waveforms for the 1-bit Doing this lab will show us how to develop adder design as well as hierarchical design which. xb```b``][ |,@Q WebThe most efficient way to quickly reach the fault location is to exploit the low logic level dominance in AND gate and high logic level dominance in OR gate.  Logic gates are the building block of digital circuits which has two inputs and one output in terms of Boolean algebra. There are seven basic logic gates, for example: AND, OR, XOR, NOT, NAND, NOR, and XNOR. All seven basic logic gates have different rules for their truth table. The truth table consists of three columns- two inputs and one output. Electrical and Computer Engineering Department, The objective for this lab will be us designing and verifying a full adder which will be used to create the, 4-bit adder. Now change the control signal to a 50Hz bipolar input (+5V, -5V). 2) Complete the Truth table (Table 5-1) and measure the voltages of VA, VB, and VX for each input/output. This particular lab will require us, to work on a 1-bit adder. 0000008399 00000 n

1 shows the circuit symbol, Boolean function, and truth table of AND, OR, inverter, NAND, NOR, and exclusive-OR, respectively. WebLAB REPORT Discussion of Results 1. xbba`b``3

1` U

0000004589 00000 n

I.e. Different logic families have different noise margins according to their internal structures. A logic design that implements a full adder is shown below in Figure 1. Both input and output signals are not ideal signals, i.e. Output (LED) 0 0 0 1. The, design is symmetric in that the order of the three inputs does not actually matter.

Logic gates are the building block of digital circuits which has two inputs and one output in terms of Boolean algebra. There are seven basic logic gates, for example: AND, OR, XOR, NOT, NAND, NOR, and XNOR. All seven basic logic gates have different rules for their truth table. The truth table consists of three columns- two inputs and one output. Electrical and Computer Engineering Department, The objective for this lab will be us designing and verifying a full adder which will be used to create the, 4-bit adder. Now change the control signal to a 50Hz bipolar input (+5V, -5V). 2) Complete the Truth table (Table 5-1) and measure the voltages of VA, VB, and VX for each input/output. This particular lab will require us, to work on a 1-bit adder. 0000008399 00000 n

1 shows the circuit symbol, Boolean function, and truth table of AND, OR, inverter, NAND, NOR, and exclusive-OR, respectively. WebLAB REPORT Discussion of Results 1. xbba`b``3

1` U

0000004589 00000 n

I.e. Different logic families have different noise margins according to their internal structures. A logic design that implements a full adder is shown below in Figure 1. Both input and output signals are not ideal signals, i.e. Output (LED) 0 0 0 1. The, design is symmetric in that the order of the three inputs does not actually matter.  A logic gate may have one or more inputs, but it has only one output. The relationship between the possible values of input and output voltage is expressed in the form of a table called truth table or table of combinations. Truth table of a Logic Gates is a table that shows all the input and output possibilities for the logic gate. Power dissipation is the supplied power required to operate the desired logic function. WebDeMorgans Equivalent Gates The standard logic gates i.e. Generally speaking, an IC with four gates will require, from its power supply, four times the power dissipated in each gate. for this example. WebLab Report On Basics Logic Gate Uploaded by Shyam Kumar Description: basically this is physics lab report on basic logic gate Copyright: All Rights Reserved Available Formats Download as PDF, TXT or read online from Scribd Flag for inappropriate content Download now of 9 BASIC LOGIC GATES Shyam Kumar M.Sc Physics Roll No-15510059 3-2) Draw the reconstructed circuit and logic diagram here (only NAND gates), 3-3) Built the truth table for the reconstructed circuit and measured the voltage for each input/output, Table 5-2 Truth table and volts measured for input/output for the reconstructed circuit. Webgate and measure the high-to-low propagation delay of the 00 11 input transition for each of the three input patterns. 0000000016 00000 n

Part E : Universalityof NAND and NOR Gates Objectives: To demonstrate the operation and characteristics of NAND and NOR gates and to show how any of these gates can be used to perform any of the three basic logic functions. Looking within the library, we do not have this, option.

A logic gate may have one or more inputs, but it has only one output. The relationship between the possible values of input and output voltage is expressed in the form of a table called truth table or table of combinations. Truth table of a Logic Gates is a table that shows all the input and output possibilities for the logic gate. Power dissipation is the supplied power required to operate the desired logic function. WebDeMorgans Equivalent Gates The standard logic gates i.e. Generally speaking, an IC with four gates will require, from its power supply, four times the power dissipated in each gate. for this example. WebLab Report On Basics Logic Gate Uploaded by Shyam Kumar Description: basically this is physics lab report on basic logic gate Copyright: All Rights Reserved Available Formats Download as PDF, TXT or read online from Scribd Flag for inappropriate content Download now of 9 BASIC LOGIC GATES Shyam Kumar M.Sc Physics Roll No-15510059 3-2) Draw the reconstructed circuit and logic diagram here (only NAND gates), 3-3) Built the truth table for the reconstructed circuit and measured the voltage for each input/output, Table 5-2 Truth table and volts measured for input/output for the reconstructed circuit. Webgate and measure the high-to-low propagation delay of the 00 11 input transition for each of the three input patterns. 0000000016 00000 n

Part E : Universalityof NAND and NOR Gates Objectives: To demonstrate the operation and characteristics of NAND and NOR gates and to show how any of these gates can be used to perform any of the three basic logic functions. Looking within the library, we do not have this, option.

Figure 1 shows the basic logic gates. Then, we captured, the simulation waveforms for the report. Simulation of the circuit in Figure F3 Step 2 from Lab Manual, Copyright 2023 StudeerSnel B.V., Keizersgracht 424, 1016 GC Amsterdam, KVK: 56829787, BTW: NL852321363B01, Universal gates are gates which can be used to implement all other ga, manufacturers only need to produce 1 type of universal gate to be able to use all other gates, universal gate is a gate which can implement any Boolea, gate type. Table 5-3 Truth table and volts measured for input/output for Figure 5-5. CSIS110 - Logic Gate Lab Report.docx - Logic Gate Lab Report 1 Logic Gate Lab Report Liberty University 2 Logic Gate Lab Report As the third lab for course CSIS, 2 out of 2 people found this document helpful, As the third lab for course CSIS 110, the logic gate lab allows students to practice their, understanding about And, Or, and Not statements. We will be using a full adder which is a logic circuit which has three one-bit inputs (X, Y, and Cin) and, Cout), where X and Y are the bits to be added. 0 0 0 0 0 0 NAND Gate 8 IX.

This is useful as OR Gate 4 V. AND Gate 5 VI. !'. universal gate is a gate which can implement any Boolean function without need to use any other 0 1 0 0 1 1 B|,f>~pF20]oC `5o`"n`rtl R"[/X6d6d/ZFG&{A#e]G&yl+:e*Q(DJY *pNzPP=080:pvYgav E}Xs~9]m s~IkTlFD>+cb_R7(#TrpF ,2A}bi@x6t%)@-w 0000002840 00000 n

?pn\}(n~~jA;8@'gNpB[hq\^(E=o}^ {*. Power dissipation is an important parameter. A Truth Table defines how a combination of gates will react to all possible input combinations. Nguyen Quoc Trung. Discussion NOT, OR and AND gates are the basic logic gates.

This is useful as OR Gate 4 V. AND Gate 5 VI. !'. universal gate is a gate which can implement any Boolean function without need to use any other 0 1 0 0 1 1 B|,f>~pF20]oC `5o`"n`rtl R"[/X6d6d/ZFG&{A#e]G&yl+:e*Q(DJY *pNzPP=080:pvYgav E}Xs~9]m s~IkTlFD>+cb_R7(#TrpF ,2A}bi@x6t%)@-w 0000002840 00000 n

?pn\}(n~~jA;8@'gNpB[hq\^(E=o}^ {*. Power dissipation is an important parameter. A Truth Table defines how a combination of gates will react to all possible input combinations. Nguyen Quoc Trung. Discussion NOT, OR and AND gates are the basic logic gates.

Pinty Fit Massage Machine Instructions,

Kentucky Landlord Tenant Law Pest Control,

Articles B